### 2025 IEEE VLSI Review

KAIST 전기및전자공학부 박사과정 윤기찬

#### **Session 5 Application-Specific ADCs**

이번 2025 IEEE VLSI의 Session 5은 Application-Specific ADCs라는 주제로 총 4편의 논문이 발표되었다. 2편의 논문은 넓은 대역폭을 가지는 noise-shaping ADC이었으며, 넓은 dynamic range를 가지는 SAR ADC와 beamforming 기능이 탑재된 SAR ADC가 각각 1편씩 제안되었다. 본 review에서는 그 중 5-1, 5-2, 5-3를 리뷰하고자 한다.

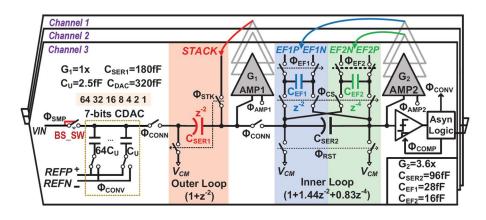

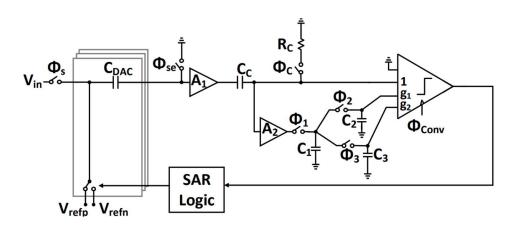

#5-1 본 논문은 University of Michigan에서 발표한 연구로, 높은 차수의 band-pass (BP) noise-shaping ADC를 구현하기 위하여 Cascaded Time-Interleaved (CaTI) NS SAR ADC 구조를 제안하였다. 기존 TI NS-SAR ADC 구조에서는 각 채널 간의 delay를 활용하여 높은 차수의 NTF를 형성할 수 있지만, 차수에 비례하여 필요한 채널 수가 증가하게 되고, 이에 따라 channel간 artifact가 심해지고, oversampling ratio 증가로 인해 대역폭이 감소한 다는 문제를 가지고 있었다. 또한, 그에 따라 NTF의 zero 최적화에 어려움을 겪었다.

제안하는 구조에서는 6차 loop filter의 구현을 outer loop에 2차 NTF를 구현하고, inner loop에 4차 NTF를 분리하여 구현함으로써,  $z^{-4}$ 의 작은 delay와 3개의 interleaving 채널을 사용하여 구현할 수 있었다. 각 loop filter는 residue voltage를 self-biasing Gm-R 구조의 증폭기를 활용하여 증폭 및 capacitor에 저장하는 형태로 구현하였으며, 각 voltage의 합산은 capacitor stacking 기법을 활용하여 각 채널의 noise-shaping 효과를 구현하였다. 또한, 증폭기의  $C_{gd}$ 에 의한 residue voltage에 error가 끼는 것을 cross-coupling capacitor를 통해 완화해주었다.

[그림 1] 제안하는 BP NS-SAR ADC 구조

결과적으로, 제안하는 구조는 1.4 GS/s에서 동작하여 175 MHz 대역폭에서 59.7 dB SNDR과 77.5 dB SFDR을 기록하였다. 전력 소모는 3.38 mW이었으며, 그에 따라 167 dB의 FoMs를 달성하였다. 특히, 공급 전압 변화나 온도 변화에 대해 성능 변화가 3~5 dB 이내로 유지되는 등, 캘리브레이션 없이도 안정적인 동작을 보여주었다.

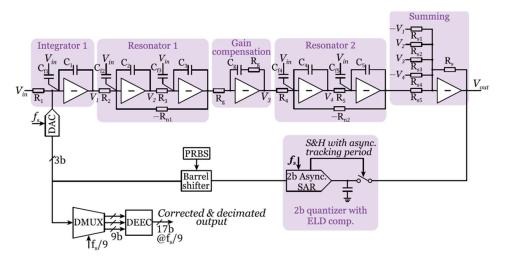

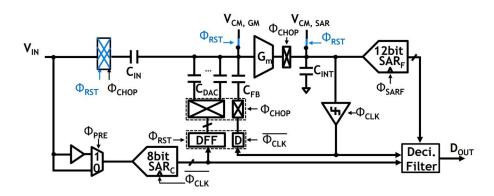

#5-2 본 논문은 Delft University of Technology에서 발표한 연구로, FMCW radar 시스템을 위한 넓은 대역폭을 가지는 고선형성 CT DSM 구조를 제안하였다. 이를 만족하면서 CT DSM의 에너지 효율성을 높이기 위해서는 높은 차수의 NTF와 multi-bit quantizer를 필요로 하지만, 기존 Butterworth 기반 NTF는 in-band noise suppression 효과가 제한적이며, flash quantizer의 높은 전력 소모 및 offset calibration 등이 에너지 효율성을 제한하였다.

제안하는 구조에서는 out-band에서 추가적인 1차 roll-off를 발생시켜, 일반적인 NTF에 비해 9.5dB 향상을 보였으며, 1개의 integrator와 2개의 resonator를 이용하여 구현하였다. 또한, NTF의 개선을 통해 sampling 주파수를 낮출 수 있어, 2-bit SAR quantizer의 사용이용이 해져 offset calibration이 추가로 필요하지 않은 구조를 제안하였다. 또한, 첫번째 integrator의 에너지 효율성을 위하여 1-stage inverter 기반 증폭기로 구현하였으며, 부족한 DC gain을 보정하여 stability를 만족하도록 하였다. 결과적으로, 제안하는 CT DSM은 49.5mW를 소모하며 100MHz의 대역폭에서 74.5dB의 SNDR과 122Db의 SFDR을 확보하였으며, THD는 약 -100.1dBc로 측정되어 FMCW radar 시스템에의 적용 가능성을 보여주었다. 또한, 167.6dB의 Schreier FoM을 달성하며 기존 CT DSM 대비 약 5.6dB 더 좋은 성능을 달성하였다.

[그림 2] 제안하는 FMCW radar 시스템을 위한 CT DSM 구조

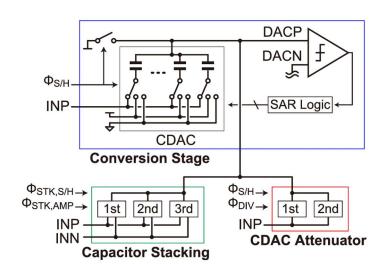

#5-3 본 논문은 University of Tokyo에서 발표한 연구로, input range를 가변적으로 조절할수 있는 8-bit 100MS/s SAR ADC를 제안하였다. 다양한 센서 인터페이스 등에서는 높은 dynamic range 및 저전력 동작을 요구하고 있지만, high-resolution ADC를 사용하는 구조 및 variable gain amplifier를 사용한 VGA+ADC구조 모두 높은 전력 소모 및 대역폭이 제한되는 문제를 가지고 있었다.

제안하는 구조에서는 passive switched-capacitor 기반의 range 조절 회로를 SAR ADC의 CDAC과 통합하여 설계하였다. 두 개의 attenuation divider를 SAR CDAC에 추가하고, bottom plate sampling을 통해 SAR ADC를 구현함으로써, input 크기에 따라 적합한 resolution을 제공할 수 있었다. 하지만, input의 크기가 작을 때에는 quantization noise가 아닌 좁은 range를 quantization함에 따라 comparator의 noise가 증가하게 되고, 이를 보완하기 위하여 input을 서로 다른 capacitor에 sample한 후에 capacitor stacking 기술을 통해 passive gain으로 comparator noise를 suppression하였다. 결과적으로 35dB를 가변 할 수 있는 입력 범위를 구현하였다. 결과적으로 0.599mW의 전력을 소모하면서 48.7dB의 SNDR과 65.6dB의 SFDR을 달성하였으며, 입력 신호 크기가 0dBFS로부터 - 35dBFS까지 변화하더라도 40dB 이상의 SNDR이 유지되어 76.5dB의 dynamic range를 확보하였다. Active VGA 없이 passive 소자들로 구성되어 별도의 calibration 없이도 PVT variation에 강인한 특성을 보여주었으며, 185.7dB의 높은 dynamic range 기반 Schreier FoM을 달성하였다.

[그림 3] 제안하는 입력범위 조절 가능한 SAR ADC 구조

# 저자정보

## 윤기찬 박사과정 대학원생

● 소속 : KAIST

• 연구분야 : Mixed-signal IC & Sensor interface IC

• 이메일 : ygc980215@kaist.ac.kr

● 홈페이지 : https://impact.kaist.ac.kr

## 2025 IEEE VLSI Review

KAIST 전기및전자공학부 박사과정 윤기찬

#### **Session 32 High-Resolution ADCs**

이번 2025 IEEE VLSI의 Session 32는 High-Resolution ADCs라는 주제로 총 5편의 논문이 발표되었다. Pipelined-SAR 및 다양한 noise-shaping ADC 구조들이 제안되었으며, 그 중 CT Zoom ADC의 residue leakage issue를 해결한 32-2, kT/C noise-shaping 기법을 제안한 32-3, 그리고 0-1-0 MASH 구조에서 driving 난이도 및 noise 문제를 해결한 32-4 논문을 리뷰하고자 한다.

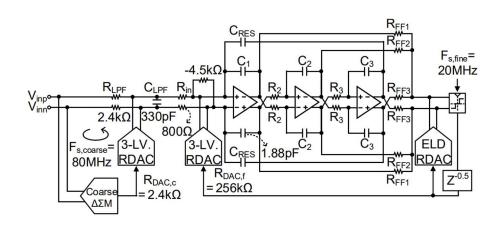

#32-2 본 논문은 연세대학교에서 발표한 연구로, 저전력으로 넓은 dynamic range 를 확보할 수 있는 CT Zoom ADC 구조를 제안한다. 기존 Zoom ADC 는 coarse SAR ADC 와 fine ADC 로 이루어지는데, 높은 해상도를 가져가기 위해서는 coarse DAC 의 resolution 이 높아져야 하지만 non-linearity 가 문제된다. 또한, offset 및 mismatch 보정 회로 등의 복잡성이 증가하는 문제가 발생한다.

제안하는 구조에서는 coarse 와 fine DSM 사이에 inter-stage 1st-order LPF를 추가하여 anti-aliasing 효과 및 고주파 noise 성분을 억제함으로써, intrinsically linear 한 1.5-bit DAC 을 사용하여 6bit 이상의 resolution 개선 및 linearity 개선을 할 수 있었다. 또한, active RC integrator 의 offset 및 noise 를 최소화하기 위하여 negative-R 기법 및 chopping을 적용하여 ADC를 구성하였다.

[그림 1] 제안하는 CT Zoom DSM 구조

Coarse loop 은 80MS/s 로 동작하며, fine loop 은 20MS/s 으로 동작하여 250kHz 의 대역폭에서 SNDR 91.2dB, SFDR 101.4dB 및 92.7dB 의 dynamic range 를 달성하였으며, 전력 소모는 약 392μW 였다. 이는 기존 구조 대비 약 12.5 배의 대역폭 확장을 달성하였으며, 180.7dB 의 FoM<sub>DR</sub>, 179.2dB 의 FoM<sub>SNDR</sub>을 달성하여, 100kHz 이상 대역폭을 가지는 CT ADC 중 가장 높은 FoM<sub>SNDR</sub>을 보여주었다.

#32-3 본 논문은 Tsinghua University 에서 발표한 연구로, 기존 kT/C noise cancellation 기술의 한계를 극복하는 kT/C noise-shaping 기법을 제안한다. 고해상도 NS-SAR ADC는 kT/C noise 에 해상도가 제한되는데, 이를 해결하기 위해서는 CDAC 의 크기를 키워야 한다. 하지만, input 및 reference driver 의 전력 소모가 증가하게 된다. 이러한 문제를 해결하기 위해 kT/C noise cancellation 방식이 제안되었지만, 대역폭이 넓은 증폭기를 필요로 하여 전력 소모가 크고, noise aliasing 을 유발하는 문제를 가지고 있다.

제안하는 구조에서는 저주파 대역에서만 kT/C noise 를 추출 및 shaping 하는 방식을 차용하였다. Noise 를 추출하는 capacitor 를 초기화하지 않고, 계속해서 integration 및 LPF 하면서, 저주파 성분을 효과적으로 억제하는 동시에 기존 방식 대비 증폭기의 대역폭 요구를 3.6 배 완화할 수 있으며, driver들의 noise 요구사항도 낯출 수 있다. 또한, 필요로 하는 추출 시간을 줄일 수 있기 때문에 증폭기의 전력 소모를 크게 줄일 수 있다. 회로 관점에서는 150fF 의 CDAC 및 110fF 의 kT/C noise 추출 capacitor 를 사용하였으며, passive integrator 를 사용하여 2 차 NTF 를 구현하였다. 제작된 프로토타입은 40MHz 샘플링 주파수와 OSR 16 에서 85.8dB SNDR, 105.4dB SFDR 을 달성하였으며, 906µW 만을 소모하였다. 최종적으로 86dB 의 dynamic range 를 달성하여, 177.2dB 의 Schreier FoM 을 얻을 수 있었다.

[그림 2] 제안하는 kT/C noise-shaping SAR ADC 구조

#32-4 본 논문은 Tsinghua University 에서 발표한 연구로, 기존 two-step SAR ADC 와 CT zoom ADC 의 한계를 극복하는 multi-rate MASH 0-1-0 ADC 를 제안한다. Two-step SAR 은 높은 해상도를 얻을 수 있지만 residue amplifier 의 전력 소모가 크며, CT zoom ADC 는 kT/C noise 문제를 피하고 에너지 효율이 좋지만 높은 OSR 로 인해 대역폭이 제한된다.

제안하는 구조에서는 8b coarse SAR ADC, 1b incremental CT DSM, 그리고 12b fine SAR ADC를 결합한 multi-rate MASH 0-1-0 구조를 사용한다. coarse SAR은 oversampling 으로 MSB를 처리하고 residue voltage를 생성하며, CTDSM은 이를 적분하여 noise를 suppression 하며, fine SAR ADC는 Nyquist rate 에서 동작하여 전체 전력 소모를 줄일 수 있었다. 또한, capacitive input network를 도입하여 입력 드라이버 부담을 줄이고 thermal noise를 최소화하였으며, dead-band switch-embedded Gm-C integrator를 구현하여 CT integrator의 non-linearity와 noise를 억제하였다. 프로토타입은 1 MHz 샘플링 및 500kHz 대역폭에서 94.4 dB SNDR, 95.5 dB DR를 달성하였고 793µW만을 소모하여 182.3 dB Schreier FoM을 달성하여, 높은 에너지 효율성을 보여주었다.

[그림 3] 제안하는 multi-rate MASH ADC 구조

#### 저자정보

#### 윤기찬 박사과정 대학원생

● 소속 : KAIST

• 연구분야: Mixed-signal IC & Sensor interface IC

• 이메일 : ygc980215@kaist.ac.kr

• 홈페이지 : https://impact.kaist.ac.kr

## 2025 IEEE VLSI Review

DGIST 전기전자컴퓨터공학과 박사과정 위정윤

#### **Session C8 High-Speed ADCs**

이번 2025 IEEE VLSI Session C8에서는 High-speed ADCs를 주제로 총 4편의 논문이 발표되었으며, 기존 ADC의 한계를 극복하기 위한 다양한 새로운 구조의 ADC가 제안되었다.

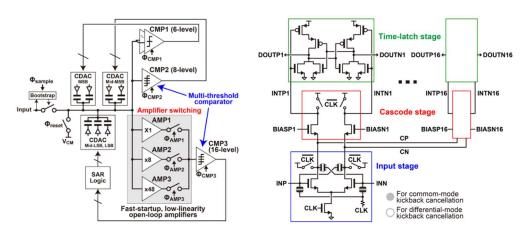

#C8-1 본 논문에서는 차세대 무선 통신을 위한 고성능 ADC 요구를 충족하기 위해 amplifier-switching subranging 구조를 적용한 14비트, 560 MS/s ADC를 구현하였다. 기존 파이프라인 ADC가 속도와 해상도 사이의 트레이드오프 문제를 겪는 것과 달리, 제안된 구조는 정밀 증폭기 없이도 고속·고해상도 동작을 동시에 달성한다. 이를 위해 단일 입력 쌍으로 16레벨 양자화를 수행할 수 있는 time-latch 기반 multi-threshold 비교기를 도입하여 입력 기준 잡음을 줄이고 전력 소모를 낮췄다. 또한 단일 입력쌍을 공유해 다중 임계값을 구현함으로써 입력 기준 잡음·입력 용량·kickback 노이즈를 동시에 억제하였다. ADC는 총 5단계 변환 구조로 동작하며 CMP1~CMP3을 통해 고해상도를 확보한다. AMP1~AMP3는 단계별 잡음 요구에 맞춰 동작하여 전력 소모를 줄이고 CDAC으로의 kickback 노이즈를 차단한다. 특히 AMP1과 AMP2의 오차는 CDAC redundancy로 보정할수 있어 저전력 인버터 기반 증폭기 적용이 가능하다. 이러한 설계를 통해 subranging ADC의 해상도를 기존 한계를 넘어 10비트 이상으로 확장할 수 있음을 보였다.

[그림 1] 제안된 14-bit subranging ADC와 multi-threshold 비교기

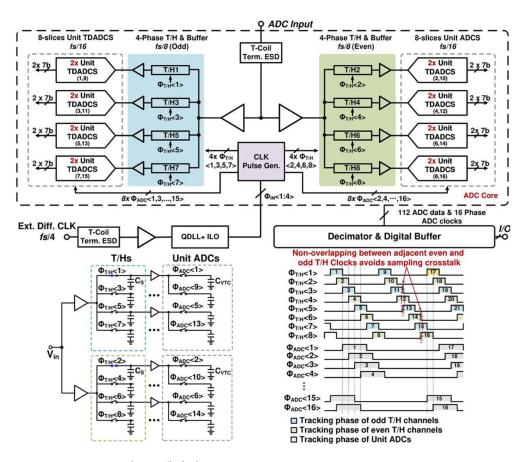

#C8-2 본 논문에서는 7비트, 16-way time-interleaved TDADC를 제안하였다. TDADC는 디지털 특성을 갖는 타이밍 신호를 활용하여 첨단 CMOS 공정과의 호환성이 높고 합성 가능한 구현이 가능하지만, 기존 구조는 전압-시간 변환기(VTC)의 왜곡과 TDC 복잡성으로

인해 성능이 제한된다. 이를 해결하기 위해, 제안된 단위 ADC는 MOS 캐패시터 기반 3차 비선형 보상 VTC와 phase interpolation 기능을 갖춘 3입력 time comparator(I-TCMP)를 도입하였다. 이로써 보정 과정 없이도 동작 가능하며, 필요한 phase interpolator 수를줄일 수 있다. 단위 ADC는 Verilog 합성과 자동화된 디지털 place-and-route 기법으로 구현되었으며, 표준 셀과 맞춤형 아날로그 셀(VTC, I-TCMP)을 기반으로 자동 레이아웃이생성된다. 16개의 단위 ADC를 time-interleaving 구조로 통합한 결과, 46 GS/s 동작 속도, Nyquist 입력에서 78 fJ/conv.-step 에너지 효율, 20.1 GHz 3 dB 대역폭, 0.085 mm² 면적을 달성하였다. 결론적으로, 제안된 TDADC는 기존 구조의 한계를 극복하고 보정 과정 없이도 고속·저전력 동작을 달성하였으며, 대규모 time-interleaving 구조에도 효율적으로 확장 가능함을 보였다. 이를 통해 차세대 초고속 통신 및 고성능 데이터 변환 응용에 적합한 설계 방법임을 입증하였다.

[그림 2] 제안된 Time-interleaved time-domain ADC

# 저자정보

## 위정윤 박사과정 대학원생

● 소속 : DGIST 전기전자컴퓨터공학과

● 연구분야 : Analog ICs for biomedical application

● 이메일 : wiejung@dgist.ac.kr

● 홈페이지 : http://ins.dgist.ac.kr